Heterogeneous Integration

Morning Session: AI for Power Efficient and High Bandwidth Interconnect Systems

Future of AI Hardware Enabled by Advanced Packaging

Wednesday, October 8, 2025

11:00am - 11:25am MT

Location: West Building, 100 Level, Room 105 BC

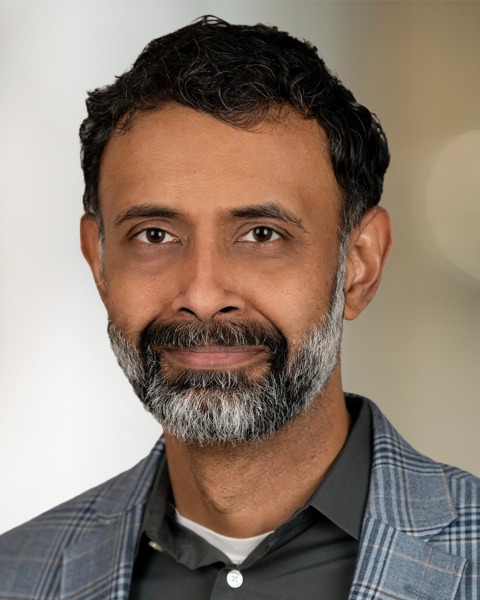

Raja Swaminathan

CVP of Heterogeneous Integration Technologies

AMD

Austin, TX, United States

Speaker (HI)(s)

Chiplet architectures are becoming foundational to the continued economic and power-efficient scaling of AI hardware and edge computing. As Moore’s Law slows, the convergence of system integration and advanced packaging has emerged as a critical enabler at the intersection of technology and architecture. This keynote will explore how heterogeneous integration—spanning 2.5D and 3D hybrid bonded architectures—is driving AMD’s industry-leading roadmap to optimize power, performance, area, and cost (PPAC). Beyond packaging, the talk will highlight the broader system-level innovations required to integrate diverse chiplets into cohesive, high-performance modules. Topics will include chiplets for AI, system integration challenges, interconnect strategies, and solutions for large-scale chiplet-based systems.